# DP84422 Dynamic RAM Controller Interface Circuit for the 68000/008/010 CPU(s)

## **General Description**

The DP84422 is a new Programmable Array Logic (PAL®) device, that replaces the DP84322, designed to allow an easy interface between the Motorola 68000 family of processors and the National Semiconductor DP8409A, DP8429, or DP8419 DRAM controller.

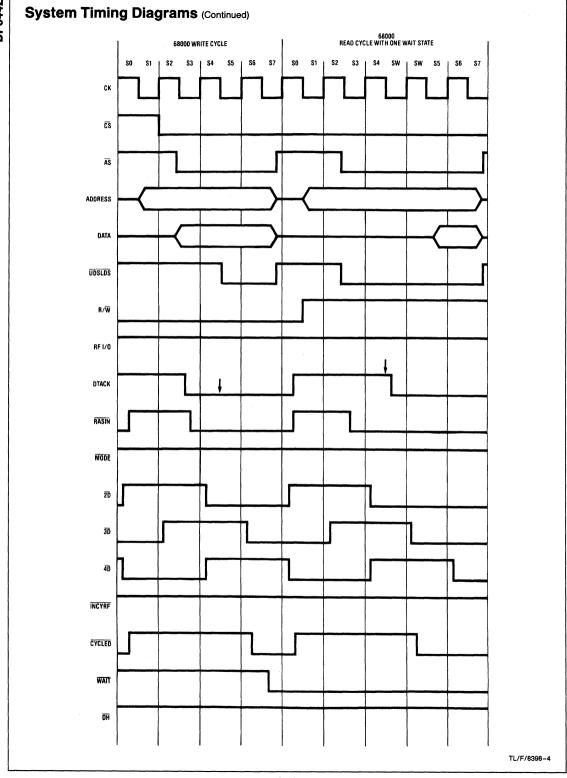

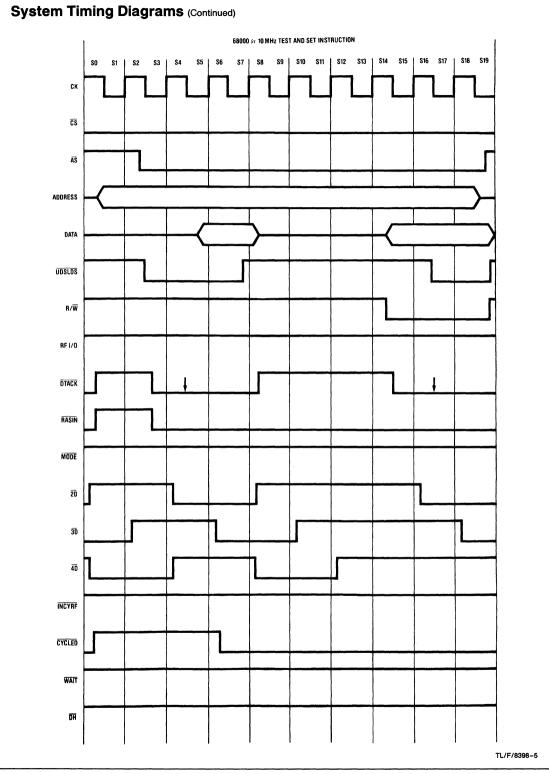

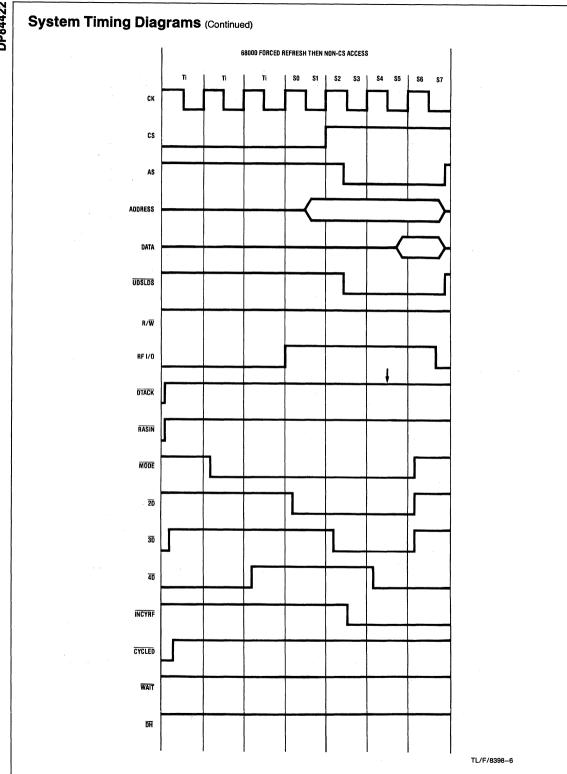

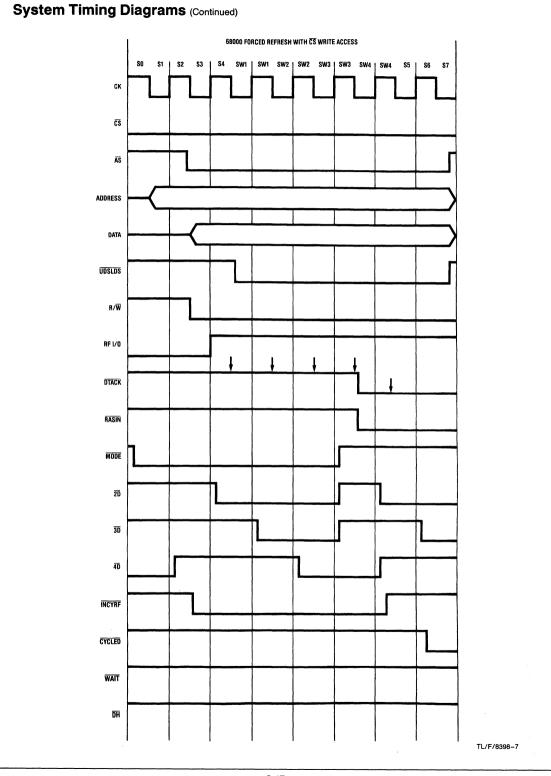

The new DP84422 supplies all the control signals needed to perform memory read, write, read modify write (as in the Test and Set, "TAS", instruction), and refresh and work with the 68000 family of processors up to 12.5 MHz. Logic is also included to insert WAIT states, if wanted, into the microprocessor READ or WRITE cycles when using fast CPUs.

#### **Features**

■ Provides a 3-chip solution for the 68000 family, dynamic RAM interface (DP8409A or DP8419, DP84422, and clock divider).

- Works with all 68000 family speed versions up to 12.5 MHz.—(68008; 68000; and 68010).

- Operation of 68000 processor at 10 MHz with no WAIT states

- Controls DP8409A or DP8419 Mode 5 accesses, hidden refreshes and Mode 1 Forced Refreshes automatically.

- Inserts WAIT states in READ or WRITE cycles automatically depending on when WAIT is low, or if chip select becomes active during a forced Refresh cycle.

- Uses a standard National Semiconductor PAL part (DMPAL16R4A).

- The PAL logic equations can be modified by the user for his specific application and programmed into any of the PALs in the National Semiconductor family, including the new very high speed PALs ("B" PAL parts).

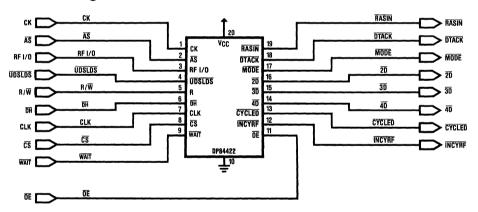

## **Connection Diagram**

TL/F/8398-1

Order Number DP84422J or DP84422N See NS Package J20A or N20A

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Operating Programming

Off-State Output Voltage

Operating Programming 5.5V 12V

Supply Voltage, V<sub>CC</sub> Input Voltage

7V 5.5V 12V 12V

Storage Temperature Range

-65°C to +150°C

## **Recommended Operating Conditions**

| Symbol          | Parameter                                     |      |     | Units |        |     |

|-----------------|-----------------------------------------------|------|-----|-------|--------|-----|

|                 | Parameter                                     | Min  | Тур | Max   | Office |     |

| V <sub>CC</sub> | Supply Voltage                                | 4.75 | 5   | 5.25  | V      |     |

| t               | Width of Clock                                | Low  | 15  | 10    |        | ns  |

| τ <sub>W</sub>  |                                               | High | 15  | 10    |        | 110 |

| t <sub>su</sub> | Setup Time from Input<br>or Feedback to Clock |      | 25  | 16    |        | ns  |

| t <sub>h</sub>  | Hold Time                                     |      | 0   | -10   |        | ns  |

| TA              | Operating Free-Air Temperature                |      | 0   | 25    | 75     | °C  |

| T <sub>C</sub>  | Operating Case Temperature                    |      |     |       |        | °C  |

## Electrical Characteristics Over Recommended Operating Temperature Range

| Symbol           | Parameter                    | Test Conditions                                                         |                               | Min | Тур   | Max   | Units |

|------------------|------------------------------|-------------------------------------------------------------------------|-------------------------------|-----|-------|-------|-------|

| V <sub>IH</sub>  | High Level Input Voltage     | !                                                                       |                               | 2   |       |       | V     |

| V <sub>IL</sub>  | Low Level Input Voltage      |                                                                         |                               |     |       | 0.8   | ٧     |

| V <sub>IC</sub>  | Input Clamp Voltage          | V <sub>CC</sub> = Min, I <sub>I</sub> = -18 mA                          |                               |     | -0.8  | -1.5  | ٧     |

| V <sub>OH</sub>  | High Level Output Voltage    | V <sub>CC</sub> =Min<br>V <sub>IL</sub> =0.8V<br>V <sub>IH</sub> =2V    | I <sub>OH</sub> = -3.2 mA COM | 2.4 | 2.8   |       | v     |

| V <sub>OL</sub>  | Low Level Output Voltage     | V <sub>CC</sub> = Min<br>V <sub>IL</sub> = 0.8V<br>V <sub>IH</sub> = 2V | I <sub>OL</sub> =24 mA COM    |     | 0.3   | 0.5   | ٧     |

| lozh             |                              | V <sub>CC</sub> =Max                                                    | V <sub>O</sub> =2.4V          |     |       | 100   | μΑ    |

| lozL             | Off-State Output Current     | $V_{IL} = 0.8V$<br>$V_{IH} = 2V$                                        | V <sub>O</sub> =0.4V          |     |       | -100  | μΑ    |

| l <sub>l</sub> . | Maximum Input Current        | V <sub>CC</sub> = Max, V <sub>I</sub> = 5.5V                            |                               |     |       | 1     | mA    |

| Iн               | High Level Input Current     | V <sub>CC</sub> = Max, V <sub>I</sub> = 2.4V                            |                               |     |       | 25    | μΑ    |

| I <sub>I</sub> L | Low Level Input Current      | V <sub>CC</sub> = Max, V <sub>I</sub> = 0.4V                            |                               |     | -0.02 | -0.25 | mA    |

| los              | Output Short-Circuit Current | V <sub>CC</sub> =5V                                                     | V <sub>O</sub> =0V            | -30 | -70   | -130  | mA    |

| lcc              | Supply Current               | V <sub>CC</sub> = Max                                                   |                               |     | 120   | 180   | mA    |

## **Switching Characteristics** Over Recommended Ranges of Temperature and V<sub>CC</sub> V<sub>CC</sub>=5V $\pm$ 10% Commercial: T<sub>A</sub>=0 to 75°C, V<sub>CC</sub>=5V $\pm$ 5%

| Parameter                   | Test Conditions<br>R1, R2                                                                                                                               |                                                        | Units     |                                                        |                                      |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------|--------------------------------------------------------|--------------------------------------|

|                             |                                                                                                                                                         | Min                                                    | Тур       | Max                                                    | Office                               |

| Input or Feedback to Output | CL=50 pF                                                                                                                                                |                                                        | 15        | 25                                                     | ns                                   |

| Clock to Output of Feedback |                                                                                                                                                         |                                                        | 10        | 15                                                     | ns                                   |

| Pin 11 to Output Enable     |                                                                                                                                                         |                                                        | 10        | 20                                                     | ns                                   |

| Pin 11 to Output Disable    | C <sub>L</sub> =5 pF                                                                                                                                    |                                                        | 11        | 20                                                     | ns                                   |

| Input to Output Enable      | C <sub>L</sub> =50 pF                                                                                                                                   |                                                        | 10        | 25                                                     | ns                                   |

| Input to Output Disable     | C <sub>L</sub> =5 pF                                                                                                                                    |                                                        | 13        | 25                                                     | ns                                   |

| Maximum Frequency           |                                                                                                                                                         | 25                                                     | 30        |                                                        | ns                                   |

|                             | Input or Feedback to Output Clock to Output of Feedback Pin 11 to Output Enable Pin 11 to Output Disable Input to Output Enable Input to Output Disable | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | Parameter | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | Parameter   R1, R2   Min   Typ   Max |

- \* SERIES DAMPING RESISTERS

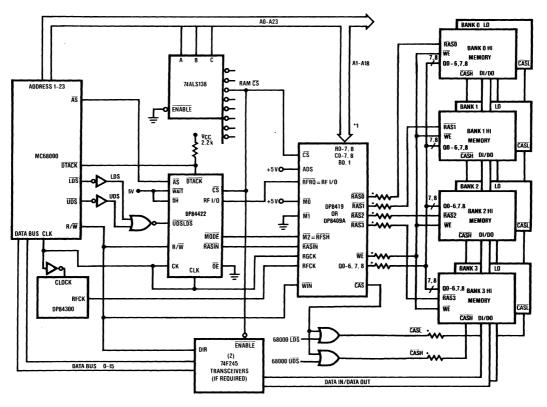

- \*1 TIE UNUSED ADDRESS LINES TO VCC

This circuit provides direct support of the 68000 Test and Set Instruction using PAGE MODE DRAMs.

TL/F/8398-2

## **Mnemonic Description**

INPUT SIGNALS "CLK", "CK" This is the 68000 CPU clock. 1) 2) "ĀS" This is the 68000 address strobe pin. This signal also tells when the 68000 is in a cycle. 3) "CS" This is the chip select signal for the DP8409A "R" This is the READ/WRITE pin from the 4) 68000. 5) "RFIO" This is the RFIO, used as refresh request, from the DP8409A. "WAIT" 6) This pin allows the insertion of 1 WAIT state in a CS Access cycle if low. As an example: if the user wants 1 WAIT state in READ accesses but 0 WAIT states in WRITE accesses he can invert the "R/W" input to this input. 7) "UDSLDS" This input was produced by inverting the two terms UDS and LDS and then logically "NOR"ing them together. This input is low whenever one or both UDS or LDS are low. This pin is used in order to support the 68000 "TAS" instruction. This signal is used in the "DTACK" PAL output. This input allows the user to disable 8) "DH"

This input allows the user to disable the DP8409A/19 hidden refresh, when low, provided he also ties " $\overline{\text{CS}}$ " low on the DP8409A/19. When this input is low " $\overline{\text{RASIN}}$ " is only brought low when a " $\overline{\text{CS}}$ " access (" $\overline{\text{CS}}$ " input to PAL low) is in progress

9) "<del>OE</del>"

Must be tied low to enable DP84422 outputs.

#### **OUTPUT SIGNALS**

1) "CYCLED"

This signal goes low once a hidden refresh or an access has been done as indicated by  $\overline{\text{2DLY}}$  and  $\overline{\text{3DLY}}$  being low. This signal goes high once the cycle is over as indicated by  $\overline{\text{AS}}$  going high. See also " $\overline{\text{DH}}$  input

2) "RASIN"

This signal goes low following  $\overline{AS}$  during an access or hidden refresh. See also " $\overline{DH}$ " input.

"DTACK"

This signal causes WAIT states to be inserted into the 68000 processor cycles if it is not low a setup time before S4 falling clock edge.

4) "INCYRF"

This signal indicates that an access has been requested during a forced refresh cycle. This signal is used to insert WAIT states during the forementioned condition or to prevent a "non-CS" access cycle from automatically starting.

5) "MODE"

This signal is used to pull the DP8409A pin M2 low in order to go to mode 1 to do a forced refresh.

This signal is an internal delay.

6) "<u>2DLY</u>" 7) "3DLY"

This signal is an internal delay. This signal is an internal delay.

8) "4DLY" This

#### **Functional Description**

The following description applies to both the DP8409A, DP8429, and the DP8419 dynamic RAM controllers.

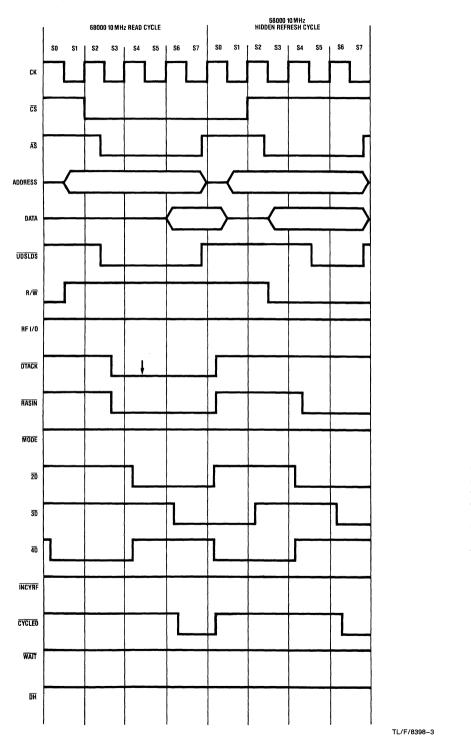

A memory cycle starts when chip select ( $\overline{CS}$ ) and address strobe ( $\overline{AS}$ ) are true.  $\overline{RASIN}$  is supplied from the DP84422 to the DP8409A dynamic RAM controller, which then supplies a  $\overline{RAS}$  signal to the selected dynamic RAM bank. After the necessary row address hold time, the DP8409A switches the address outputs to the column address. The DP8409A then supplies the required  $\overline{CAS}$  signal to the DRAM. In order to do byte operations it is suggested that the user provide external logic, as shown in the system block diagram, to produce a HIGH CAS and a LOW CAS. To differentiate between a READ and a WRITE, the R/ $\overline{W}$  signal from the CPU is used.

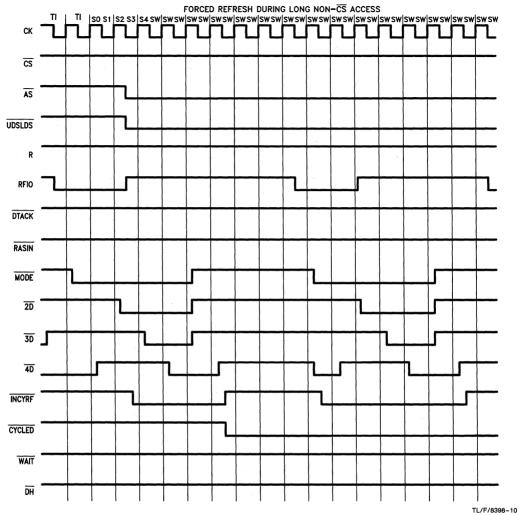

A refresh cycle is started by one of two conditions. The refresh cycle caused by the first condition is called a hidden refresh. This occurs when refresh clock (RFCK) is high, CS is not true, and RASIN goes low. Here the CPU is accessing something else in the system and the DRAM can be refreshed at that time, thereby being transparent to the CPU. The second type of refresh is called forced refresh. This occurs if no hidden refresh was performed while RFCK was high. When RFCK transitions low a refresh request (RFRQ) is generated. If there is not a DRAM access in progress the DP84422 will force a refresh by putting the DP8409A into mode 1 (automatic forced refresh mode). If the CPU tries to access the DRAM during a forced refresh cycle WAIT states will be inserted into its cycles until the forced refresh is over and the DRAM RAS precharge time has been met. Then the pending DRAM access will be allowed to take place.

The DP84422 also allows forced refreshes to take place during long accesses of other devices. For instance, if EEPROM takes several microseconds to write to, the DRAM will still be refreshed while that access is in progress.

In a standard memory cycle, the access can be slowed down by one clock cycle to accommodate slower memories or allow time to generate parity. This is accomplished by inserting a WAIT state into the processor access cycle. The DP84422 can insert WAIT states into either READ cycles, WRITE cycles, READ MODIFY WRITE cycles, or both READ and WRITE cycles or the READ and WRITE portion of a READ MODIFY WRITE cycle. The extra WAIT state will not appear during the hidden refresh cycle, so faster devices on the CPU bus will not be affected.

During a Test and Set instruction  $\overline{\text{CAS}}$  is generated twice while  $\overline{\text{RAS}}$  is low. In order for this instruction to execute properly Page Mode DRAMs must be used.

## **System Interface Description**

All members of the Motorola 68000 family of processors are able to use the DP84422.

RASIN during a READ cycle will always start at the beginning of the "S3" processor cycle. The user must guarantee that  $\overline{\text{CS}}$  is valid a minimum of 34 ns before RASIN becomes valid, unless the PAL " $\overline{\text{DH}}$ " input is low and the DP8409A/19 " $\overline{\text{CS}}$ " input is tied low (hidden refresh disabled).

Several critical parameters in this application involve the input system CLOCK and the ADDRESS STROBE,  $\overline{AS}$ . These parameters become most critical at higher frequencies (10 MHz and above) where it is suggested that they are directly connected to the corresponding pins of the Motorola 68000 family ICs.

This section of the data sheet goes through the calculation of the "t<sub>RAC</sub>" ( $\overline{\text{RAS}}$  access time) and "t<sub>CAC</sub>" ( $\overline{\text{CAS}}$  access time) required by the DRAM for the 68000 family CPUs to operate at a particular clock frequency without introducing wait states into the processor access cycles. Both "t<sub>RAC</sub>" and "t<sub>CAC</sub>" must be considered in determining what speed DRAM can be used in a particular system design. The DRAM chosen must meet both the "t<sub>RAC</sub>" and "t<sub>CAC</sub>" parameters calculated. In order to determine the "t<sub>RAC</sub>" and "t<sub>CAC</sub>" needed the DP8419 and fast PALs ("B" type PALs) timing parameters were used. If the user is using the DP8408A/09A or a slower PAL device he should substitute their respective delays into the equation below.

Most all of the calculations contained in this note use "RAHS" = 1 (15 ns guaranteed minimum row address hold time). Calculations only used "RAHS" = 0 (25 ns guaranteed minimum row address hold time) when the calculated access time from RAH exceeded 200 ns. This is because DRAMs can be found with row access times up to 150 ns that require only 15 ns row address hold times.

The calculated " $t_{RAC}$ " and " $t_{CAC}$ " may differ from the actual system values depending upon the external circuitry used to produce " $\overline{CASH}$ " and " $\overline{CASL}$ ". The DP8409A/19 " $\overline{RASIN}$ — $\overline{CAS}$ " low will be approximately 10–15 ns less than the value given in the data sheet because of the small loading on the DP8409A/19 " $\overline{CAS}$ " output. The external circuitry needed to produce " $\overline{CASH}$ , L" should be loaded such that the column address (from DP8409A/19 is valid when " $\overline{CASH}$ , L" goes low. For this reason " $\overline{RASIN}$ — $\overline{CASH}$ , L" may be longer than the value used in the " $t_{RAC}$ ,  $t_{CAC}$ " calculations, and therefore may give a smaller " $t_{RAC}$ ,  $t_{CAC}$ " then was calculated.

## **EXAMPLE DRAM TIMING CALCULATIONS**A) 8 MHz 68000, No WAIT States

- #1) RASIN low = S0 + S1 + AS low (maximum) + "B"

PAL combinational output delay maximum = 125 +

60 + 15 = 220 ns maximum

- #2)  $\overline{RASIN}$  to  $\overline{RAS}$  low = 20 ns maximum

- #3) RASIN to CAS low = 80 ns (DP8419 RASIN CAS low) 3 ns (load of 72 DRAMs instead of 88 DRAMs speced in data sheet) = 77 ns

- #4) 74F245 transceiver delay = 7 ns maximum

- #5) CPU data setup time = 15 ns minimum

"t<sub>RAC</sub>" =

$$(S0 + S1) + (S2 + S3) + (S4 + S5) + S6$$

(min)

-  $\#1 - \#2 - \#4 - \#5$

=  $125 + 125 + 125 + 55 - 200 - 20 - 7 - 15$

=  $188$  ns

"t<sub>CAC</sub>" =  $(S0 + S1) + (S2 + S3) + (S4 + S5) + S6$  (min)

-  $\#1 - \#3 - \#4 - \#5$

$$= 125 + 125 + 125 + 55 - 200 - 77 - 7 - 15$$

Therefore the DRAM chosen should have a " $t_{RAC}$ " less than or equal to 188 ns and a " $t_{CAC}$ " less than or equal to 131 ns. Standard 150 ns DRAMs meet this criteria.

The minimum RAS PRECHARGE TIME will be approximately one and one half clock periods = 125 + 55 = 180 ns.

The minimum  $\overline{\text{CAS}}$  PRECHARGE TIME will be approximately one and one half clock periods plus 35 ns (minimum  $t_{\text{RICL}} - t_{\text{RICH}}$  for the DP8409-2)=125+55+35=215 ns.

The minimum  $\overline{RAS}$  PULSE WIDTH will be approximately two clock periods -5 ns (maximum  $t_{RPDL}-t_{RPDH}$  for the DP8409-2) =250-5=245 ns.

The minimum  $\overline{\text{CAS}}$  PULSE WIDTH will be approximately two clock periods -70 ns (maximum  $t_{\text{RICL}} - t_{\text{RICH}}$  for the DP8409-2) = 250 - 70 = 180 ns.

The smallest pulse widths are generated during WRITE cycles since RASIN during WRITE cycles starts later than RASIN during READ cycles.

If one inserted a WAIT state in READ cycles the DRAM column access times, the  $\overline{CAS}$  pulse width, and the  $\overline{RAS}$  pulse width would be increased by one clock period (125 ns in this case). A WAIT state in WRITE cycles would just increase the  $\overline{RAS}$  and  $\overline{CAS}$  precharge by one clock period.

#### B) 10 MHz 68000, No WAIT states

- #1)  $\overline{\text{RASIN}}$  low = S0 + S1 +  $\overline{\text{AS}}$  low (maximum) + "B" PAL combinational output delay maximum = 100 + 55 + 15 = 170 ns maximum

- #2) RASIN to RAS low = 20 ns maximum

- #3) RASIN to CAS low = 80 ns (DP8419 RASIN CAS low) 3 ns (load of 72 DRAMs instead of 88 DRAMs speced in data sheet) = 77 ns

- #4) 74F245 transceiver delay = 7 ns maximum

- #5) CPU data setup time = 10 ns minimum

"t<sub>RAC</sub>" =

$$(S0 + S1) + (S2 + S3) + (S4 + S5) + S6$$

(min)

$- #1 - #2 - #4 - #5$

=  $100 + 100 + 100 + 45 - 170 - 20 - 7 - 10$

=  $138$  ns

"t<sub>CAC</sub>" =  $(S0 + S1) + (S2 + S3) + (S4 + S5) - S6$  (min)

Therefore the DRAM chosen should have a " $t_{RAC}$ " less than or equal to 138 ns and a " $t_{CAC}$ " less than or equal to 81 ns. Standard 120 ns DRAMs meet this criteria.

The minimum  $\overline{RAS}$  PRECHARGE TIME will be approximately one and one half clock periods = 100+45=145 ns.

The minimum  $\overline{\text{CAS}}$  PRECHARGE TIME will be approximately one and one half clock periods plus 35 ns (minimum  $t_{\text{RICL}} - t_{\text{RICH}}$  for the DP8419) = 100 + 45 + 35 = 180 ns.

The minimum  $\overline{\text{RAS}}$  PULSE WIDTH will be approximately two clock periods -5 ns (maximum  $t_{\text{RPDL}} - t_{\text{RPDH}}$  for the DP8419) = 200 -5 = 195 ns.

The minimum  $\overline{CAS}$  PULSE WIDTH will be approximately two clock periods – 50 ns (maximum  $t_{RICL}-t_{RICH}$  for the DP8419) = 200 – 50 = 150 ns.

The smallest pulse widths are generated during WRITE cycles since RASIN during WRITE cycles starts later than RASIN during READ cycles.

If one inserted a WAIT state in READ cycles the DRAM column access times, the  $\overline{\text{CAS}}$  pulse width, and the  $\overline{\text{RAS}}$  pulse width would be increased by one clock period (100 ns in this case). A WAIT state in WRITE cycles would just increase the  $\overline{\text{RAS}}$  and  $\overline{\text{CAS}}$  precharge by one clock period.

#### Interpreting the DP84422 PAL Equations

The boolean equations for the DP84422 were written using the standard PALASM™ format. In other words the equation:

"IF (VCC) RASIN = INCY \* MODE \* 4D \* R" will mean:

The output "RASIN" (see pin list for DP84422) will be active low (inverted RASIN) when the output "INCY" is low (making INCY high) AND the output "MODE" is high AND the output " $\overline{4D}$ " is low (making 4D high) and the input R/ $\overline{W}$  is low (making  $\overline{R}$  high).

PAL16R4A : FAST PAL

NEW PAL FOR THE MOTOROLA 68000 PROCESSOR

(WORKS UP TO 12.5MHZ)

CK /AS RFIO /UDSLDS R /DH CLK /CS /WAIT GND

/OE /INCYRF /CYCLED /4DLY /3DLY /2DLY /MODE /DTACK /RASIN VCC

IF (VCC) RASIN =

CS\*/INCYRF\*AS\*/MODE\*4DLY\*/CYCLED\*/CLK+

/CS\*/INCYRF\*AS\*/MODE\*2DLY\*/CYCLED\*/DH+ CS\*INCYRF\*AS\*/MODE\*4DLY\*/CYCLED\*/CLK+

CS\*RASIN\*/MODE\*AS+ RASIN\*/MODE\*2DLY

:Start RASIN

:RASIN for Hidden RFSH :Start RASIN after RFSH

:Hold RASIN valid :Hold RASIN valid

IF (VCC) CYCLED =/MODE\*2DLY\*3DLY\*/4DLY+

CYCLED\*AS+ /MODE\*CYCLED\*/CLK+

/CS\*AS\*/MODE\*/2DLY\*/3DLY\*/4DLY

:Start "CYCLED", does not allow

; glitch after refresh ;End on rising edge of CLK

:Start during long accesses of other

: devices

IF (VCC) INCYRF =MODE\*AS+

INCYRF\*4DLY\*AS

:Set Access during Refresh

IF (CS) DTACK = AS\*/WAIT\*/R\*/MODE\*/CLK+

AS\*WAIT\*/R\*/MODE\*2DLY\*/CLK+ UDSLDS\*/WAIT\*R\*/MODE\*/CLK+ UDSLDS\*WAIT\*R\*/MODE\*2DLY\*/CLK+

DTACK\*2DLY\*/MODE+

DTACK\*AS\*RASIN\*/MODE\*/CYCLED+

DTACK\*AS\*/R\*/MODE

:Hold it while 4DLY is low

:0 WAIT's for WRITE :1 WAIT for WRITE

:0 WAIT's for READ

;1 WAIT for READ

;Continue DTACK

:Continue DTACK

:Continue DTACK in RMW

: cycle

MODE : = /RFIO\*/AS\*/CYCLED\*/RASIN+

;For IDLE states or beginning ; states of 68000 cycle

CS\*/RFIO\*AS\*CYCLED\*/2DLY\*/3DLY\*/RASIN+

;For RFSH during long cycles

; of other devices

MODE\*/3DLY+ MODE\*/4DLY

2DLY := MODE\*/4DLY+

/INCYRF\*AS\*/CYCLED\*/MODE\*/3DLY\*4DLY+

CS\*INCYRF\*AS\*/CYCLED\*/MODE\*/3DLY\*4DLY+

/MODE\*2DLY\*/3DLY+ CS\*WAIT\*AS\*/MODE\*2DLY\*3DLY\*/4DLY+

CS\*AS\*/R\*CYCLED\*/MODE\*/2DLY\*/3DLY\*/4DLY

:Start 2DLY

;Start 2DLY after RFSH

:Make 2DLY longer :Start second 2DLY for the TAS instruction

3DLY : = 2DLY\*/4DLY 4DLY := 3DLY+

/AS\*/MODE+

/CS\*/RFIO\*AS\*CYCLED\*/2DLY\*/3DLY\*/RASIN\*/MODE ; Need for beginning of forced refresh to

; inhibit "ZDLY"

FIGURE 1. Equations for New 68000 PAL That Supports the 68000 "TAS" Instruction

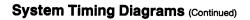

## **System Timing Diagrams**

TL/F/8398-8

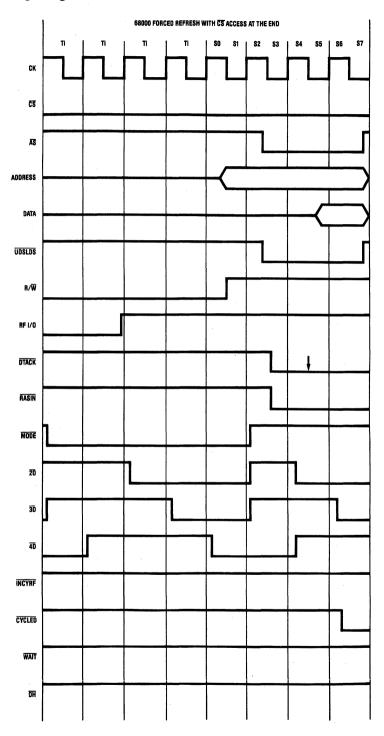

TL/F/8398-9

INCYRF

CYCLED

WAIT

## System Timing Diagrams (Continued)